이를 통해 현재 가장 복잡한 SoC의 프로토타이핑 및 에뮬레이션은 물론, AI, 머신러닝, 비디오 프로세싱 및 센서 융합에 사용되는 새로운 복잡한 알고리즘들을 개발할 수 있다.

VU19P는 당시 업계에서 가장 큰 FPGA였던 20nm 버텍스 울트라스케일 440 이전 세대 FPGA 보다 1.6배 더 큰 것이다.

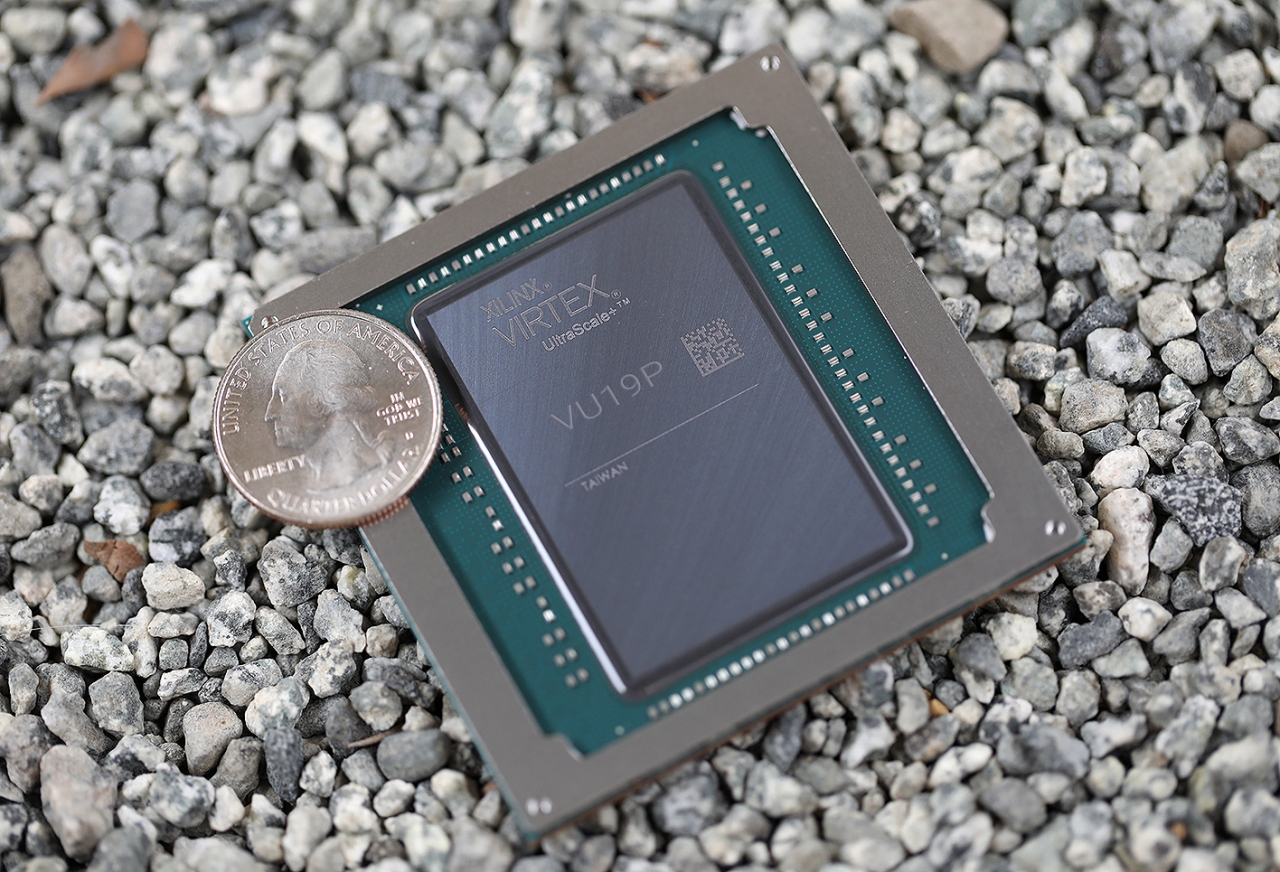

자일링스(Xilinx)는 세계에서 가장 큰 FPGA인 버텍스(Virtex) 울트라스케일+(UltraScale+™) VU19P를 출시하고, 16나노(nm) 기반 버텍스 울트라스케일+ 제품군을 확장한다고 21일(현지시각) 밝혔다. 이를 통해 현재 가장 복잡한 SoC의 프로토타이핑 및 에뮬레이션은 물론, 인공지능, 머신러닝, 비디오 프로세싱 및 센서 융합에 사용되는 새로운 복잡한 알고리즘들을 개발할 수 있다.

350억개의 트랜지스터를 갖춘VU19P는 단일 디바이스 상에서 전례 없이 가장 높은 로직 밀도와 가장 많은 수의 I/O를 제공함으로써미래의 최첨단 ASIC 및 SoC 기술은 물론, 테스트 및 측정, 컴퓨팅, 네트워킹, 항공우주, 방위 관련 애플리케이션 분야의 에뮬레이션 및 프로토타이핑이 가능하다.

VU19P는 새로운 FPGA 표준을 수립한 것으로 보인다. 900만 개에 이르는 시스템 로직 셀을 비롯해 초당 최대 1.5테라비트의 DDR4 메모리 대역폭 및 초당 최대 4.5테라비트의 트랜시버 대역폭과 더불어 2,000개 이상의 사용자 I/O를 갖추고 있다. VU19P는 당시 업계에서 가장 큰 FPGA였던 20nm 버텍스 울트라스케일 440 이전 세대 FPGA 보다 1.6배 더 큰 것으로 제품은 2020년 가을에 일반에 공급될 예정이다. (아래는 Virtex® UltraScale + ™ VU19P를 소개 영상)

자일링스의 제품 라인 마케팅 및 관리 책임자인 서밋 샤(Sumit Shah) 수석 매니저는 “개발자는 ASIC이나 SoC를 적용하기 전에 VU19P를 사용하여 하드웨어 유효성 검사를 가속화하고, 소프트웨어 통합을 시작할 수 있다.”고 말하고, “이 제품은 세계 기록을 보유한 3세대 FPGA이다. 첫 번째는 버텍스-7 2000T이고, 2세대는 버텍스 울트라스케일 VU440, 그리고 이번에 버텍스 울트라스케일+ VU19P에 이르게 되었다.하지만 이는 단지 실리콘 기술에 국한되는 것은 아니며, 이를 지원하는 검증된 견고한 툴 플로우와 IP도함께 제공된다.”고 밝혔다.

한편 VU19P는 광범위한 디버그 및 가시성 툴과 IP 세트가 지원되기 때문에 고객들은 차세대 애플리케이션및 기술을 신속하게 설계하고 검증할 수 있는 포괄적인 개발 플랫폼으로 활용할 수 있다. 개발자는 하드웨어 및 소프트웨어에 대한 공동 유효성 검사를 통해 실제 부품이 공급되기 전에 소프트웨어를 불러오고, 사용자 지정 기능들을 구현할 수 있다. 또한 자일링스 비바도 디자인 수트(Vivado Design Suite)를 이용해 디자인 플로우를 함께 최적화할 수 있기 때문에 비용 및 테이프-아웃(Tape-Out) 리스크를 줄이고, 효율을 높이며, 시장출시 시간을 단축할 수 있다.