파나소닉이 개발한 40nm 저항형 메모리 공정 기술과 UMC의 CMOS 공정 기술과 통합

파나소닉 세미컨덕터 솔루션즈(Panasonic Semiconductor Solutions 대표 고야마 가즈히로 Kazuhiro Koyama)가 중국 유나이티드 마이크로일렉트로닉스 코퍼레이션(United Microelectronics Corporation, 이하 UMC 대표 포원옌 Po Wen Yen)과 차세대 40nm 저항형 메모리(ReRAM)의 양산 공정 공동 개발에 관해 지난 2일 합의했다고 7일 밝혔다.

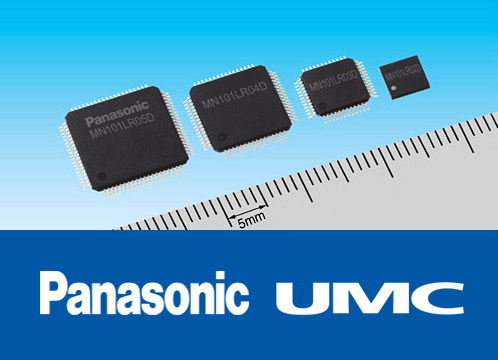

저항형 메모리는 현재 널리 사용되고 있는 플래시 메모리와 마찬가지로 비휘발성 메모리의 한 종류다. 저항형 메모리는 간단한 구조, 고속 처리, 저전력 소비를 특징으로 하며, 파나소닉은 지난 2013년에 180nm 공정을 이용해 저항형 메모리 양산을 시작했고, 현재 헬스케어, 웨어러블 디바이스 등의 저전력 애플리케이션을 위해 8비트 마이크로컴퓨터 MN101LR 시리즈를 공급하고 있다. 파나소닉은 40nm 공정 메모리 배열의 높은 안정성을 시험하고 입증한 최초의 회사다.

공동 프로젝트를 진행하기로 합의함에 따라 파나소닉이 개발한 40nm 저항형 메모리 공정 기술을 UMC가 가진 높은 안정성의 CMOS 공정 기술과 통합할 수 있게 됐다. 이에 따라 IC 카드, 착용 가능 단말기, 사물인터넷 기기에 널리 쓰이는 다양한 시스템 장치에 플래시 메모리 대신 내장 메모리로 적용 가능한 저항형 메모리를 위한 공정 플랫폼을 만들 수 있게 됐다.

파나소닉은 신규 40nm 공정을 이용해 2018년 샘플을 출하하고, 업계 최초로 양산을 시작할 계획이다. 파나소닉과 UMC는 공동 개발한 저항형 메모리 공정 플랫폼을 전세계 반도체 제조업체 및 공급업체에 제공할 예정이다.

이 공동 프로그램에 관해 파나소닉의 사장 고야마 가즈히로는 “파나소닉은 저항형 메모리의 양산을 최초로 시작한 회사인 만큼, 저항형 메모리의 시장 진입을 가속화할 미세화 공정 플랫폼을 개발해 고객의 요구에 맞춘 광범위한 최적의 제품을 제공하고자 한다”고 말했다.

UMC의 수석부사장 S.C. 치엔(S.C. Chien)은 “파나소닉과 파운드리 합의를 맺게 되어 기쁘다”며 “UMC 40nm 공정의 입증된 안정성, 빠른 사이클 시간, 높은 수율 덕분에 파나소닉의 저항형 메모리는 새로이 경쟁력을 갖출 수 있게 될 것이다”고 밝혔다. 이어 “그로 인해 저항형 메모리가 광범위하게 시장에 진입하면 두 회사 모두 이익을 보게 된다”며 “우리는 파나소닉과 협력해 파나소닉의 40nm 저항형 메모리를 대량 생산할 수 있게 되기를 고대한다”고 말했다.