인공지능(AI) 머신러닝(ML) 애플리케이션을 위한 이더넷, OTN, 파이버 채널 및 독점 데이터 속도 지원

하이브리드 작업의 증가 및 네트워크의 지리적 분포로 인해 네트워크 인프라의 대역폭과 보안에 대한 수요가 증가하고 있으며, 이로 인해 보더리스 네트워킹이 재정의되고 있다.

650 그룹에 따르면 AI/ML 애플리케이션이 주도하는 400G(초당 기가비트)와 800G의 총 포트 대역폭은 연간 50% 이상 성장할 것으로 전망된다. 이러한 급격한 성장은 112G PAM4 연결로의 전환 추세를 클라우드 데이터 센터와 통신 서비스 제공업체 스위치 및 라우터를 넘어 엔터프라이즈 이더넷 스위칭 플랫폼으로 확대시키고 있다.

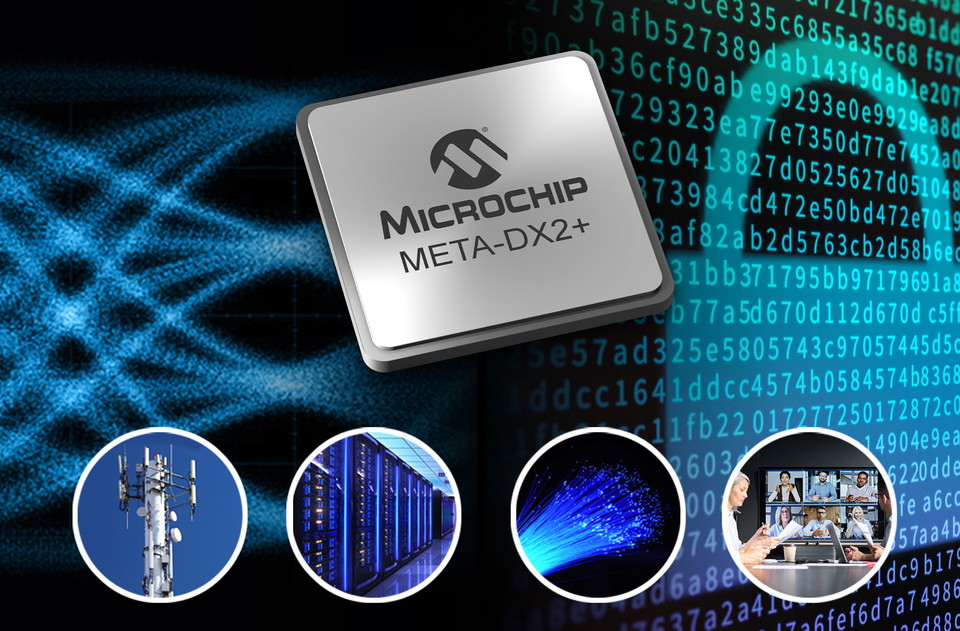

마이크로컨트롤러, 혼합 신호, 아날로그 반도체 및 플래시-IP 솔루션 분야의 선도기업 마이크로칩테크놀로지(Microchip Technology. 이하, 마이크로칩)는 이러한 시장 변화에 대응하고자 새로운 META-DX2+ PHY를 도입한 META-DX2 이더넷 PHY 포트폴리오를 새롭게 출시했다.

이 신규 제품군은 1.6T(초당 테라비트)의 회선속도 종단간 암호화 및 포트 집성(aggregation)을 통합하는 업계 최초의 솔루션으로, 엔터프라이즈 이더넷 스위치, 보안 기기, 클라우드 상호 연결 라우터 및 광전송 시스템에서 가장 작은 설치 공간을 유지하면서 112G PAM4 연결로 전환할 수 있게 해 준다.

특히, 인공지능(AI) 머신러닝(ML) 애플리케이션을 위한 이더넷, OTN, 파이버 채널 및 독점 데이터 속도 지원한다.

마이크로칩의 바박 사미미(Babak Samimi) 통신 사업부 부사장은 “마이크로칩은 이 4개의 신규 META-DX2+ 이더넷 PHY 도입을 통해 , META-DX 리타이머 및 PHY 포트폴리오로 구동되는 112G PAM4 연결로의 커넥티비티로 시장 전환을 지원하고자 최선을 다하고 있다.

마이크로칩은 META-DX2L 리타이머와 함께 리타이밍, 기어박스, 고급 PHY 기능에 이르기까지 모든 연결 요구사항을 충족하는 완벽한 칩셋을 제공한다”라며, “하드웨어 및 소프트웨어 모두에서 풋프린트 호환성을 제공하기 때문에 고객들은 엔터프라이즈, 데이터 센터, 서비스 제공업체 스위칭 및 라우팅 시스템 전반에 걸쳐 아키텍처 설계를 활용할 수 있다.

종단간 보안, 다중 속도 포트 집성과 같은 고급 기능의 경우 필요한 만큼 쓰고 지불하면 되며, 정밀 타임스탬프 기능은 소프트웨어 구독 방식으로 사용 가능하다”고 말했다.

META-DX2+의 구성 가능한 1.6T 데이터 경로 아키텍처는 고유한 ShiftIO 기능을 활용해 총 기어박스 용량 및 히트리스 2:1 보호 스위치 멀티플렉서(mux) 모드에서 경쟁사보다 두 배 이상 월등한 성능을 구현한다.

유연한 XpandIO 포트 통합 기능은 저속 트래픽을 지원할 때 라우터/스위치 포트 활용을 최적화한다. 또한 이 디바이스에는 5G 및 엔터프라이즈 비즈니스 핵심 서비스에 필요한 정확한 나노초 타임스탬프를 위한 IEEE 1588 클래스 C/D PTP(정밀 시간 프로토콜) 지원이 포함돼 있다.

마이크로칩은 풋프린트 호환 리타이머 및 암호화 옵션이 있는 고급 PHY 포트폴리오를 제공해 개발자가 공통 보드 설계 및 SDK(소프트웨어 개발 키트)를 기반으로 MACsec 및 IPsec을 추가한 디자인으로 확장 가능하도록 해준다.

650그룹 LLC의 설립자이며 기술 분석가이기도 한 알란 베켈(Alan Weckel)은 “업계가 고밀도 라우터 및 스위치를 위한 112G PAM4 직렬 에코시스템으로 전환함에 따라 회선 속도 암호화와 포트 용량의 효율적 사용에 대한 중요성이 더욱 커지고 있다.

마이크로칩의 META-DX2+ 제품군은 MACsec 및 IPsec 암호화를 가능하게 하고, 포트 집성을 통해 포트 용량을 최적화하고, 라우팅/스위칭 실리콘과 다중 속도 400G 및 800G 광학 디바이스와의 유연한 연결에 중요한 역할을 할 것이다”고 덧붙였다.

META-DX2L 리타이머와 마찬가지로 새로운 META-DX2+ PHY 시리즈는 마이크로칩의 PolarFire® FPGA, ZL30632 고성능 PLL, 오실레이터, 전압 레귤레이터 및 보다 빠른 개발을 지원하는 사전 검증된 기타 구성 요소와 함께 사용할 수 있다.

한편, META-DX2 제품군을 위한 마이크로칩 2세대 이더넷 PHY SDK는 현장에서 검증된 API 라이브러리 및 펌웨어로 개발 비용을 절감한다. SDK는 제품군 내의 모든 META-DX2L 및 META-DX2+ PHY 디바이스를 지원한다.

오픈 컴퓨팅 프로젝트(OCP: Open Compute Project) 스위치 앱스트랙션 인터페이스(SAI: Switch Abstraction Interface) PHY 확장에 대한 지원이 포함되어 있으므로, SAI를 지원하는 광범위한 NOS(네트워크 운영 체제) 내에서 META-DX2 PHY에 대한 애그노스틱 지원이 가능하다.